本文探討了服務器內存中CAS(Compare-And-Swap)操作的物理地址延遲和控制延遲之間的關系。CAS是一種原子性操作,用于在多線程環境中實現同步。物理地址延遲是指內存訪問的時間,而控制延遲是指CAS操作的執行時間。文章將介紹CAS操作的工作原理、物理地址延遲和控制延遲的定義,以及它們之間的關系。進一步討論了如何通過優化內存系統設計和硬件實現來降低CAS操作的延遲,提高服務器內存的性能和響應速度。

1. CAS操作簡介:

CAS是一種原子性操作,用于在多線程環境中實現同步。

CAS操作包括三個步驟:讀取內存值、比較內存值和期望值、根據比較結果更新內存值。

2. 物理地址延遲:

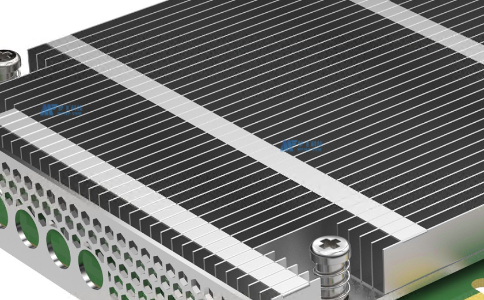

物理地址延遲是指內存訪問的時間,包括內存控制器發送請求到內存模塊、內存模塊響應請求和數據傳輸的時間。

物理地址延遲受到多種因素影響,包括內存頻率、總線帶寬、內存通道數和內存排布等。

3. 控制延遲:

控制延遲是指CAS操作的執行時間,包括CPU執行CAS指令的時間和內存子系統處理CAS操作的時間。

控制延遲受到CPU性能、內存控制器設計、總線協議和內存模塊響應速度等因素的影響。

4. 物理地址延遲與控制延遲的關系:

物理地址延遲和控制延遲是服務器內存性能的兩個關鍵指標,它們之間存在一定的關系。

物理地址延遲的增加會導致內存訪問時間延長,間接影響CAS操作的控制延遲。

5. 降低CAS操作延遲的方法:

優化內存系統設計:包括增加內存通道數、提高內存頻率、優化內存排布和總線協議等。

硬件實現優化:采用更高性能的內存控制器、優化CAS操作的處理流程和緩存設計等。

6. 實際案例與應用:

介紹一些實際服務器內存系統中CAS操作延遲優化的案例和應用實踐。

通過理解CAS操作的物理地址延遲和控制延遲之間的關系,服務器管理員可以有針對性地優化內存系統設計和硬件實現,提高CAS操作的執行效率,從而改善服務器內存的性能和響應速度。